終究,醜媳婦總是要見公婆。模擬也總是要跟測試值比較一下。

透過對於一個問題的物理模式分析,我們"猜測了"哪些東西重要予以考量和哪些不重要予以忽略。而和測試結果相當於驗證想法,和修正想法來做為下次建模的依據至於是不是完全吻合? 倒不是完全的重要,甚至是說完全一樣有一種湊答案的感覺

大致接近但略有出入其實是最合理的結果。

以此為目標,看看是不是有重要的因素被忽略了或是重複考量了或是各種可能。

透過前面一拖拉庫的測試,我們大致上可以知道各種構件對流場的影響,這次則是確認各種熱源對我們的目標,板溫,的影響。

我們總共在4個區域貼了數目不一的Thermal couple:

1. VRM

2. PCIE connector

3. CPU 往後方出線側

4. PSU

最後濃縮成4種case:

Case1: 只帶上CPU,DDR熱源並配上一個代表PCB的FR4塊

Case2: 以Case1為基礎,加上PCB因為焦耳效應產生的熱,並載入Layout線路資料

Case5: 以Case1為基礎,帶上VRM,PCH,AOC等熱源,並載入Layout線路資料

Case7: 結合Case2與Case5的熱源

結果如下

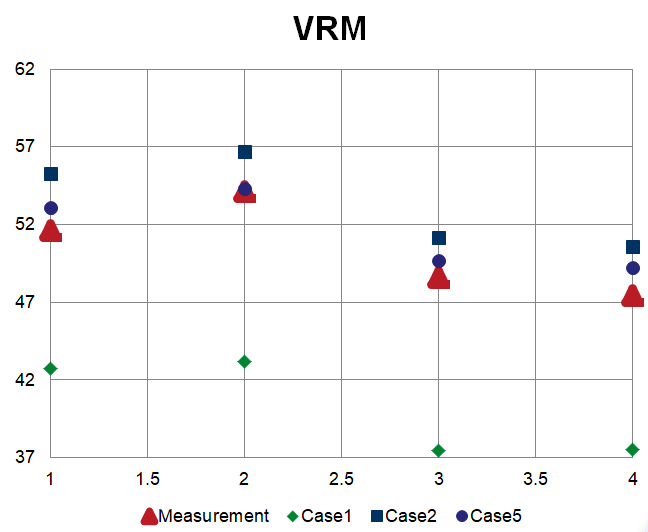

- VRM區域

首先可以看得很清楚是Case1的效果有明顯低估的現象。而在Case2與Case5的結果則是很接近。至於到底是Joule Heating的比重多呢? 還是元件的發熱比重多呢?

個人覺得應該還是元件發熱比重多一些。主要原因是我認為單純銅箔的阻抗應該會比元件內部半導體阻抗來的低,也因此銅箔發熱量應該會比元件來得低,那為什麼結果好像是Case2比Case5來的高? 比較可能的原因是SIwave在模擬的時候高估了實際工作時銅箔上面的電流。

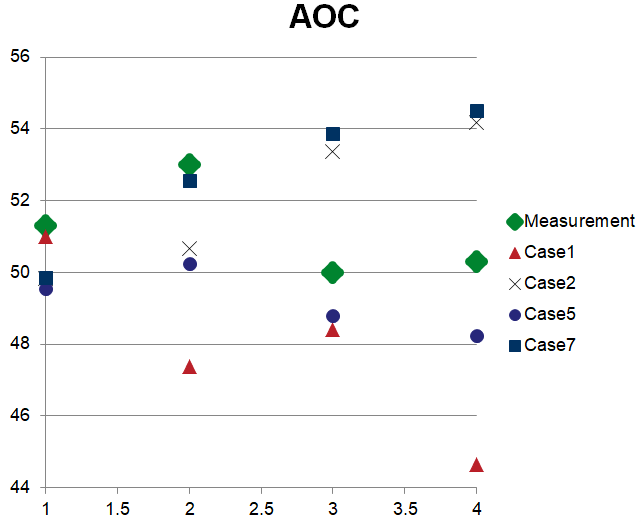

2. PCIE connector (AOC area)

Thermal couple所貼的點是分別是在PCIE connector的兩側以及前後端。

在Case7和Case1分別有著過於高估以及過於低估的問題。而Case7的原因從Case2當中透漏了出來,一樣也是在前端SIwave所填入的電流值高估了實際經過的電流所導致。而Case5的結果相對接近,則是說明在AOC區域的熱傳現象應該還是元件發熱所主導。

3. PSU

這個區域因為空間限制所以只取了一個點,位置是在gold finger後方,P12V剛進入mother board的區域。

在這一個區域倒是很明顯地由Joule Heating主導了附近的溫升,因為附近並沒有其他的熱源,同時有大電流經過該區。只要是沒有考量Joule Heating的Case都明顯低估。但是為什麼其他地區高估的電流在這個區域看似沒有太多的不良影響呢?

主要可能是因為比例的關係。在局部區域走3A你估到6A相當於增加了1倍的量,但是在1000A的PSU區域你就算多估20A其實差別也不是很大。

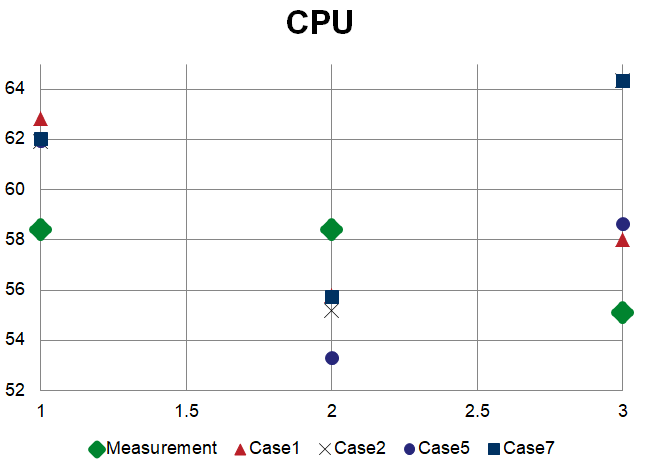

4. CPU 出線區

在CPU附近其實各種Case都沒有說得上理想的結果,但是透過Case1的結果表示不管是附近元件或是Joule Heating對他都不是影響的原因。比較有可能的狀況是Case1再搭配上導入線路資料的PCB對熱傳導有更好的描繪,其實就夠了。

總和以上結論其實會發現到因為對應到不同區域的主導對象不同,合併考量有時候反而會造成高估。因此針對重點區域選擇合適的方式是比較合理的做法。當然會有這樣的結果也是因為我們沒有辦法完全重現PCB板內的電流現象所導致。

最後,總結:

VRM區域- MOS 與 Inductor主導

AOC區域- 區域元件與板卡外露的熱(板卡大部分的熱是透過自己的風扇出去)

PSU區域- Joule Heating

CPU區域- CPU與PCB傳導